Intel Reveals Plans for a Trillion-transistor Processor by 2030

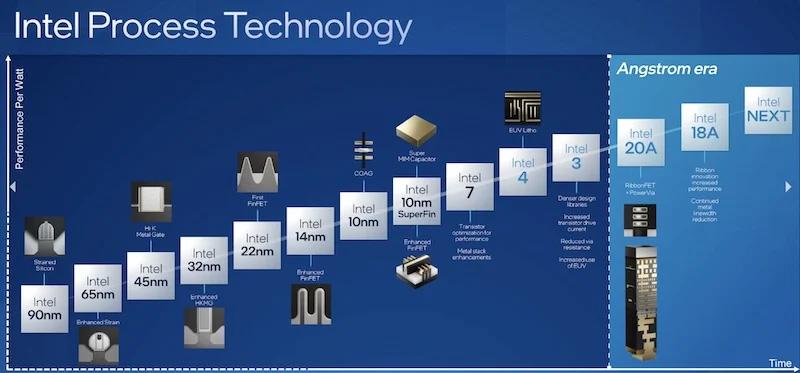

Intel has announced plans to achieve a trillion-transistor processor by 2030, ushering in the age of the Angstrom. The silicon giant made the announcement during the IEEE International Electron Devices Meeting, symbolically on the 75th anniversary of the transistor.

Intel’s Component Research Group (CRG) submitted 9 papers to highlight the various research and advances the company has made since the last meeting. The group has specifically focused on merging silicon and packaging in both 2D and 3D, advances in ferroelectric components, and improvements in power efficiency, all contributing to the trillion-transistors-by-2030 objective.

Intel’s CRG has previously been responsible for breakthroughs in the FinFet, strained silicon, and Hi-K metal gates.

Intel’s process technology roadmap. Image used courtesy of Intel. (Click image to enlarge)

Achieving a trillion-transistor processor by 2030 would be a successful continuation of Moore’s Law, which has been speculated to be reaching its theoretical limit. Increasing transistor density in a world that is relying on increasingly more capable processing capabilities is one of several strategies to keep up with demands.

In this article, we’ll review a few highlights of Intel’s showing at the 2024 IEDM.

3D Hybrid Packaging

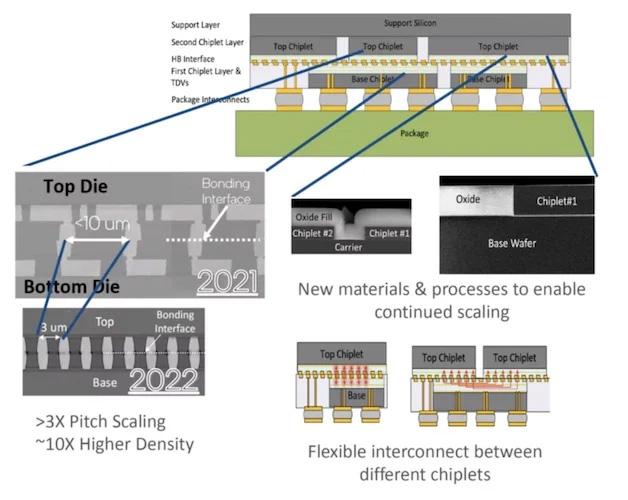

One of the key developments presented by the group is the increased density in interconnects between chiplets within a quasi-monolithic 3D packing.

At the 2021 IEDM, the group presented this architecture that featured 10 μm bonding gaps. At the 2022 event, the group reported a successful reduction to 3 μm bonding gaps, resulting in 10x increased interconnect density.

Intel has set its sights on the next 10x improvement in interconnect density. Image used courtesy of Intel. (Click image to enlarge)

This increased density also provides more flexibility for how the top and bottom chiplets are positioned relative to one another, as well as the number of chiplets in the stack.

The “quasi-monolithic” aspect comes from the idea that this chip architecture can achieve performance similar to a purely monolithic chip in which interconnects are fabricated within a single die.

Reportedly, Intel’s presentation on the topic suggests that their quasi-monolithic packaging has a road to market with manufacturing materials and processes already being defined.

Ferroelectric Components

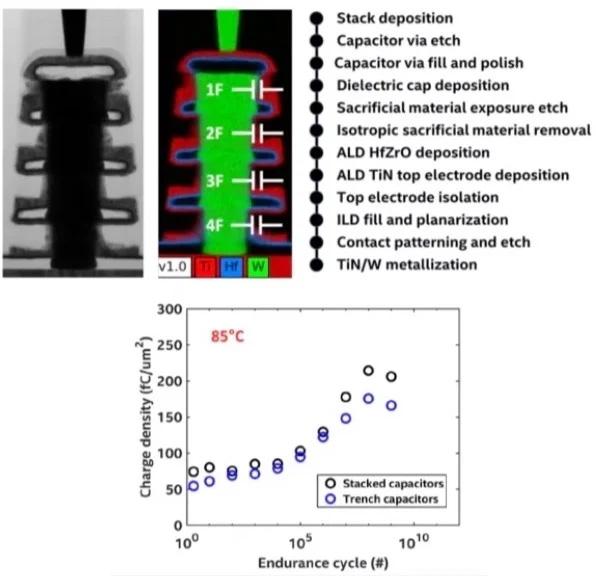

Ferroelectric memory (FeRAM) is a next generation memory component which features high speeds, large storage capacity, and persistent memory similar to non-volatile FLASH. It is composed of a transistor layer, with a ferroelectric capacitor layer on top.

During IEDM 2024, the Intel group provided a demonstration of their 3D FeRAM implementation, which is reported to be the first successful demonstration to date.

FeRAM has been presented as a possible alternative to dielectric RAM before, however it still faces challenges in achieving the same density. Intel’s 3D FeRAM has a vertically stacked architecture, with a logic layer and memory layer on top of each other. This reduces the horizontal die size, improves memory density, as well as speed, making it more competitive as an alternative.

At IEDM, Intel demonstrated that stack array capacitors matched performance with traditional ferroelectric trench capacitors. Image used courtesy of Intel

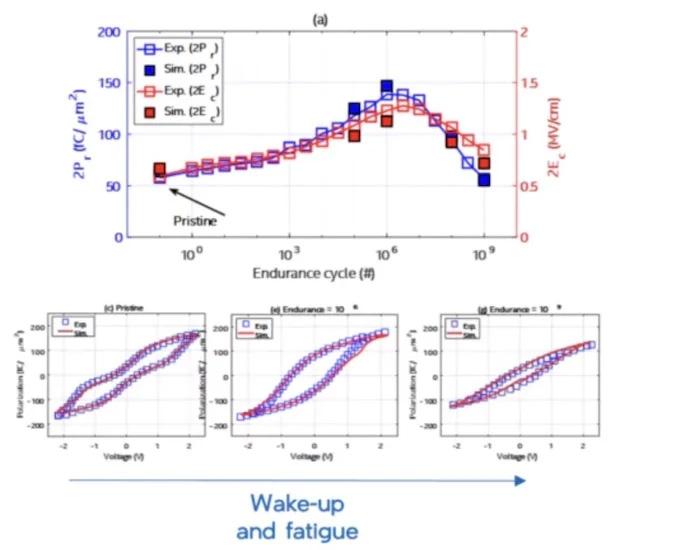

Additionally, Intel’s group has modeled ferroelectric Hafnia-based devices, specifically capturing interactions among phase transitions, mixed phases, and defects. Intel expects that this research will contribute to the development of new ferroelectric memory devices, as well as ferroelectric transistors.

These graphs show the complex cycling behavior of polycrystalline (anti-)ferro such as wake-up, fatigue, and imprint. Image used courtesy of Intel. (Click image to enlarge)

Intel and its CRG unit appear to be serious about keeping up with Moore’s Law and are coming up with creative and innovative solutions to support their trillion-transistor objectives. Their showing at the 2024 IEDM indicates they are attacking the problem from multiple angles.

Sign up to our newsletter

Receive our latest updates about our products & promotions